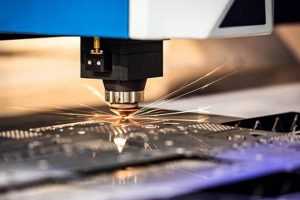

What is gate fabrication design? Gate fabrication design is the process of creating the patterns that will be used to create the gates on a semiconductor chip. These patterns are created using a variety of techniques, including photolithography, electron beam lithography, and X-ray lithography.

Editor’s Notes: Gate fabrication design is a critical step in the semiconductor manufacturing process because it determines the performance and reliability of the final product. By carefully designing the gates, manufacturers can improve the chip’s speed, power consumption, and resistance to defects.

In this guide, we will explore the different steps involved in gate fabrication design, and we will discuss the factors that must be considered when creating these patterns. We will also provide some tips for optimizing gate design to improve chip performance.

Key Differences or Key Takeaways

| Feature | Photolithography | Electron Beam Lithography | X-Ray Lithography |

|---|---|---|---|

| Resolution | 200 nm | 10 nm | 1 nm |

| Throughput | High | Low | Medium |

| Cost | Low | High | Medium |

Transition to main article topics

- The different steps involved in gate fabrication design

- The factors that must be considered when creating gate patterns

- Tips for optimizing gate design to improve chip performance

Gate Fabrication Design

Gate fabrication design is a critical step in the semiconductor manufacturing process. By carefully designing the gates, manufacturers can improve the chip’s speed, power consumption, and resistance to defects. Here are 11 key aspects of gate fabrication design:

- Resolution: The minimum feature size that can be fabricated.

- Throughput: The number of wafers that can be processed per hour.

- Cost: The cost of the equipment and materials used in gate fabrication.

- Overlay accuracy: The precision with which multiple layers of a semiconductor device can be aligned.

- Etch selectivity: The ability to remove one material without affecting another.

- Defect density: The number of defects per unit area on a semiconductor wafer.

- Electrical properties: The electrical characteristics of the gates, such as their resistance and capacitance.

- Reliability: The ability of the gates to withstand harsh operating conditions.

- Manufacturability: The ease with which the gates can be fabricated.

- Design rules: The set of rules that govern the design of gates.

- Simulation: The use of computer models to predict the performance of gates before they are fabricated.

These key aspects are all interrelated and must be carefully considered when designing gates. For example, the resolution of the lithography process will determine the minimum feature size of the gates, and the etch selectivity will determine the ability to remove the gate material without affecting the underlying substrate. By optimizing all of these aspects, manufacturers can create gates that meet the performance and reliability requirements of modern semiconductor devices.

Resolution

The resolution of the lithography process is one of the most important factors in gate fabrication design. The resolution determines the minimum feature size that can be fabricated, which in turn affects the performance and power consumption of the chip. For example, a higher resolution allows for the fabrication of smaller gates, which can improve the chip’s speed and reduce its power consumption.

The resolution of the lithography process is limited by the wavelength of the light used to expose the photoresist. Shorter wavelengths allow for higher resolution, but they are also more expensive and difficult to generate. As a result, there is a trade-off between resolution and cost.

In recent years, there has been a trend towards using shorter wavelengths for lithography. This has allowed for the fabrication of smaller gates and has helped to improve the performance and power consumption of chips. However, as the wavelength of the light used for lithography decreases, the cost and complexity of the lithography process increases.

The following table summarizes the key insights regarding the connection between resolution and gate fabrication design:

| Resolution | Gate Fabrication Design |

|---|---|

| Higher resolution allows for the fabrication of smaller gates. | Smaller gates can improve the chip’s speed and reduce its power consumption. |

| The resolution of the lithography process is limited by the wavelength of the light used to expose the photoresist. | Shorter wavelengths allow for higher resolution, but they are also more expensive and difficult to generate. |

| There is a trade-off between resolution and cost. | In recent years, there has been a trend towards using shorter wavelengths for lithography. |

The connection between resolution and gate fabrication design is a critical one. By understanding this connection, manufacturers can make informed decisions about the lithography process to use for their chips.

Throughput

Throughput is a critical factor in gate fabrication design because it determines the cost and efficiency of the manufacturing process. The higher the throughput, the more wafers that can be processed per hour, which reduces the cost per wafer. However, throughput is also affected by other factors, such as the resolution of the lithography process and the complexity of the gate design.

- Cost: Throughput has a direct impact on the cost of gate fabrication. The higher the throughput, the lower the cost per wafer. This is because the fixed costs of the manufacturing process are spread over a larger number of wafers.

- Efficiency: Throughput also affects the efficiency of the manufacturing process. A higher throughput allows manufacturers to produce more wafers in a given amount of time. This can be important for meeting production deadlines or for reducing the time-to-market for new products.

- Gate design complexity: The complexity of the gate design can also affect throughput. More complex gate designs require more processing steps, which can reduce throughput. Therefore, it is important to consider the trade-off between gate design complexity and throughput when designing gates.

- Lithography resolution: The resolution of the lithography process can also affect throughput. Higher resolution lithography processes require more time to expose and develop the photoresist, which can reduce throughput. Therefore, it is important to consider the trade-off between resolution and throughput when selecting a lithography process.

By understanding the connection between throughput and gate fabrication design, manufacturers can make informed decisions about the manufacturing process to use for their chips.

Cost

The cost of gate fabrication is a major consideration for semiconductor manufacturers. The cost of the equipment and materials used in gate fabrication can vary significantly depending on the process technology and the volume of wafers being processed. Here are some of the key cost factors to consider:

- Equipment: The cost of the equipment used in gate fabrication can be significant. This includes the cost of the lithography system, the etching system, and the deposition system. The cost of the equipment will vary depending on the resolution, throughput, and other capabilities of the system.

- Materials: The cost of the materials used in gate fabrication can also be significant. This includes the cost of the photoresist, the etch chemicals, and the deposition materials. The cost of the materials will vary depending on the type of process technology being used.

- Volume: The cost of gate fabrication can also be affected by the volume of wafers being processed. The higher the volume, the lower the cost per wafer. This is because the fixed costs of the manufacturing process are spread over a larger number of wafers.

By understanding the cost factors involved in gate fabrication, manufacturers can make informed decisions about the process technology and the volume of wafers to be processed.

Overlay accuracy

Overlay accuracy is a critical factor in gate fabrication design because it affects the performance and reliability of the final product. Overlay accuracy refers to the precision with which multiple layers of a semiconductor device can be aligned. The more precise the overlay accuracy, the better the performance and reliability of the device.

There are several reasons why overlay accuracy is important in gate fabrication design. First, overlay accuracy affects the electrical properties of the gates. If the gates are not aligned precisely, it can lead to increased resistance and capacitance, which can degrade the performance of the chip. Second, overlay accuracy affects the reliability of the gates. If the gates are not aligned precisely, it can lead to defects that can cause the chip to fail.

There are several ways to improve overlay accuracy in gate fabrication design. One way is to use a higher resolution lithography process. A higher resolution lithography process will produce smaller features, which will make it easier to align the different layers of the device. Another way to improve overlay accuracy is to use a more precise alignment system. A more precise alignment system will be able to align the different layers of the device more accurately.

By understanding the connection between overlay accuracy and gate fabrication design, manufacturers can make informed decisions about the process technology and the equipment to use for their chips.

Table: Overlay Accuracy and Gate Fabrication Design

| Overlay Accuracy | Gate Fabrication Design |

|---|---|

| Overlay accuracy affects the electrical properties of the gates. | The electrical properties of the gates affect the performance of the chip. |

| Overlay accuracy affects the reliability of the gates. | The reliability of the gates affects the reliability of the chip. |

| There are several ways to improve overlay accuracy in gate fabrication design. | By improving overlay accuracy, manufacturers can improve the performance and reliability of their chips. |

Etch selectivity

Etch selectivity is a critical factor in gate fabrication design because it determines the ability to remove one material without affecting another. This is important because the gate stack is composed of multiple layers of different materials, and it is necessary to be able to remove one layer without damaging the other layers.

- Gate patterning: Etch selectivity is used to pattern the gate by removing the gate material from the areas where it is not wanted. This is done using a lithography process to define the pattern of the gate, followed by an etching process to remove the gate material from the exposed areas.

- Spacer formation: Etch selectivity is also used to form spacers between the gate and the source/drain regions. This is done by etching the spacer material into the gate dielectric, and then using the gate as a mask to protect the source/drain regions from being etched.

- Contact etching: Etch selectivity is also used to etch contacts between the gate and the source/drain regions. This is done by etching the contact material into the gate dielectric, and then using the gate as a mask to protect the source/drain regions from being etched.

The etch selectivity of a process is determined by the chemistry of the etchant and the materials being etched. The ideal etchant will have a high etch rate for the target material and a low etch rate for the mask material. This will ensure that the target material is removed quickly and cleanly, while the mask material is protected.

Etch selectivity is a critical factor in gate fabrication design because it affects the performance and reliability of the final product. Poor etch selectivity can lead to defects in the gate stack, which can degrade the performance of the chip. Therefore, it is important to carefully consider the etch selectivity of the process when designing gates.

Defect density

Defect density is a critical factor in gate fabrication design because it affects the performance and reliability of the final product. Defects can occur during any stage of the manufacturing process, and they can range in size from atomic-scale defects to large, visible defects. Even a small number of defects can degrade the performance of a chip, so it is important to minimize defect density as much as possible.

- Gate leakage: Defects in the gate oxide can lead to gate leakage, which is a major source of power consumption in CMOS circuits. Gate leakage can also degrade the performance of the chip by increasing the delay time of the gates.

- Threshold voltage variation: Defects in the gate material can lead to threshold voltage variation, which is a variation in the threshold voltage of the gates. Threshold voltage variation can affect the performance of the chip by causing some gates to turn on prematurely or to not turn on at all.

- Early breakdown: Defects in the gate dielectric can lead to early breakdown of the gate, which can cause the chip to fail. Early breakdown is a major reliability concern for chips that are used in mission-critical applications.

There are several ways to minimize defect density in gate fabrication design. One way is to use a high-quality starting material. Another way is to use a cleanroom environment during the manufacturing process. Finally, it is important to use careful process control to minimize the number of defects that are introduced during each step of the process.

By understanding the connection between defect density and gate fabrication design, manufacturers can make informed decisions about the process technology and the equipment to use for their chips.

Electrical properties

The electrical properties of the gates, such as their resistance and capacitance, are critical factors in gate fabrication design. These properties affect the performance and power consumption of the chip, and they must be carefully controlled to ensure that the chip meets its design specifications.

The resistance of a gate is determined by the material used to make the gate and the dimensions of the gate. A thicker gate will have a higher resistance than a thinner gate, and a gate made of a more resistive material will have a higher resistance than a gate made of a less resistive material.

The capacitance of a gate is determined by the area of the gate and the distance between the gate and the substrate. A larger gate will have a higher capacitance than a smaller gate, and a gate that is closer to the substrate will have a higher capacitance than a gate that is farther from the substrate.

The resistance and capacitance of the gates are important factors in determining the delay time of the gates. The delay time is the amount of time it takes for a signal to propagate through a gate. A gate with a high resistance will have a longer delay time than a gate with a low resistance. A gate with a high capacitance will also have a longer delay time than a gate with a low capacitance.

By understanding the connection between the electrical properties of the gates and gate fabrication design, manufacturers can make informed decisions about the materials and dimensions to use for their gates. This will help them to design chips that meet their performance and power consumption requirements.

Table: Electrical Properties and Gate Fabrication Design

| Electrical Property | Gate Fabrication Design |

|---|---|

| Resistance | The resistance of a gate is determined by the material used to make the gate and the dimensions of the gate. |

| Capacitance | The capacitance of a gate is determined by the area of the gate and the distance between the gate and the substrate. |

| Delay time | The delay time of a gate is determined by the resistance and capacitance of the gate. |

Reliability

Reliability is a critical factor in gate fabrication design because it affects the lifetime and performance of the final product. Gates are subjected to a variety of harsh operating conditions, including high temperatures, high voltages, and radiation. These conditions can degrade the performance of the gates over time, and they can even cause the gates to fail. Therefore, it is important to design gates that are reliable and can withstand these harsh operating conditions.

There are several ways to improve the reliability of gates. One way is to use high-quality materials. Another way is to use a robust design that is less susceptible to failure. Finally, it is important to use careful process control to minimize the number of defects that are introduced during the manufacturing process.

By understanding the connection between reliability and gate fabrication design, manufacturers can make informed decisions about the materials, design, and process technology to use for their gates. This will help them to design chips that are reliable and can withstand the harsh operating conditions that they will encounter in the field.

Table: Reliability and Gate Fabrication Design

| Reliability Factor | Gate Fabrication Design |

|---|---|

| High temperatures | Gates can be designed to withstand high temperatures by using materials with a high melting point and by using a design that minimizes heat dissipation. |

| High voltages | Gates can be designed to withstand high voltages by using materials with a high breakdown voltage and by using a design that minimizes the electric field across the gate. |

| Radiation | Gates can be designed to withstand radiation by using materials that are resistant to radiation damage and by using a design that minimizes the exposure of the gate to radiation. |

Manufacturability

Manufacturability is a critical factor in gate fabrication design because it affects the cost and efficiency of the manufacturing process. The easier it is to fabricate the gates, the lower the cost and the higher the efficiency. There are several factors that affect the manufacturability of gates, including the design of the gates, the choice of materials, and the process technology used.

- Gate design: The design of the gates can have a significant impact on their manufacturability. Gates with complex designs can be more difficult to fabricate than gates with simple designs. For example, gates with sharp corners or small features can be more difficult to pattern and etch than gates with rounded corners or larger features.

- Choice of materials: The choice of materials can also affect the manufacturability of gates. Some materials are more difficult to etch or deposit than others. For example, gates made of refractory metals can be more difficult to etch than gates made of aluminum.

- Process technology: The process technology used to fabricate the gates can also affect their manufacturability. Some process technologies are more mature and well-established than others. For example, optical lithography is a more mature process technology than extreme ultraviolet lithography.

- Equipment and infrastructure: The availability of equipment and infrastructure can also affect the manufacturability of gates. Some equipment and infrastructure is more expensive and less accessible than others. For example, extreme ultraviolet lithography equipment is more expensive and less accessible than optical lithography equipment.

By understanding the connection between manufacturability and gate fabrication design, manufacturers can make informed decisions about the design of the gates, the choice of materials, and the process technology to use. This will help them to design gates that are easy to manufacture and cost-effective.

Design Rules

Design rules are a set of guidelines that govern the design of gates in integrated circuits (ICs). These rules are essential for ensuring that gates can be fabricated reliably and with the desired performance. Design rules are typically developed by semiconductor foundries and are based on the specific process technology used to fabricate the ICs.

- Minimum feature size: The minimum feature size is the smallest size that a feature can be fabricated on the IC. This rule is important for ensuring that gates can be patterned and etched accurately.

- Spacing rules: Spacing rules define the minimum distance between two features on the IC. These rules are important for preventing electrical shorts and ensuring that gates can be isolated from each other.

- Layout rules: Layout rules define the placement of gates and other features on the IC. These rules are important for ensuring that the IC can be fabricated efficiently and that it meets the desired performance specifications.

- Electrical rules: Electrical rules define the electrical properties of gates, such as their resistance, capacitance, and voltage limits. These rules are important for ensuring that gates can operate reliably and meet the desired performance specifications.

Design rules are a critical part of gate fabrication design. By following these rules, manufacturers can ensure that gates are fabricated reliably and with the desired performance. Design rules are constantly being updated as new process technologies are developed. This is because new process technologies can enable the fabrication of smaller features and more complex designs.

Simulation

Simulation is a critical component of gate fabrication design. By using computer models to predict the performance of gates before they are fabricated, manufacturers can identify and correct potential problems early in the design process. This can save time and money by avoiding costly mistakes in the fabrication process.

There are a number of different types of simulation tools that can be used for gate fabrication design. These tools can be used to simulate the electrical, thermal, and mechanical properties of gates. By using these tools, manufacturers can optimize the design of their gates to meet the desired performance specifications.

One of the most important benefits of simulation is that it allows manufacturers to predict the performance of gates under a variety of operating conditions. This can help to ensure that gates will operate reliably in the final product.

For example, simulation can be used to predict the delay time of a gate. This information can be used to optimize the design of the gate to meet the desired performance specifications. Simulation can also be used to predict the power consumption of a gate. This information can be used to optimize the design of the gate to reduce power consumption.

By using simulation, manufacturers can gain valuable insights into the performance of their gates before they are fabricated. This information can be used to optimize the design of the gates to meet the desired performance specifications. Simulation is a powerful tool that can help manufacturers to save time and money by avoiding costly mistakes in the fabrication process.

| Benefit | Description |

|---|---|

| Reduced time to market | Simulation can help to identify and correct potential problems early in the design process, which can save time and money by avoiding costly mistakes in the fabrication process. |

| Improved performance | Simulation can be used to optimize the design of gates to meet the desired performance specifications. |

| Reduced power consumption | Simulation can be used to predict the power consumption of a gate and optimize the design to reduce power consumption. |

| Improved reliability | Simulation can be used to predict the performance of gates under a variety of operating conditions, which can help to ensure that gates will operate reliably in the final product. |

FAQs on Gate Fabrication Design

This section provides answers to frequently asked questions (FAQs) about gate fabrication design, offering clear and concise information on this crucial aspect of semiconductor manufacturing.

Question 1: What is the significance of resolution in gate fabrication design?

Resolution refers to the minimum feature size that can be fabricated during the lithography process. Higher resolution enables the creation of smaller gates, leading to improved chip performance, reduced power consumption, and increased transistor density.

Question 2: How does throughput impact gate fabrication design?

Throughput represents the number of wafers that can be processed per hour. Higher throughput reduces the cost per wafer and improves production efficiency. However, achieving higher throughput may require trade-offs in resolution or gate design complexity.

Question 3: What role does overlay accuracy play in gate fabrication design?

Overlay accuracy ensures the precise alignment of multiple layers in a semiconductor device. High overlay accuracy is crucial for maintaining electrical properties, enhancing device reliability, and preventing defects that could compromise chip performance.

Question 4: Why is etch selectivity important in gate fabrication design?

Etch selectivity refers to the ability to remove specific materials without affecting adjacent layers. Precise etch selectivity is essential for patterning gates, forming spacers, and creating contacts between the gate and other regions of the device. Improper etch selectivity can lead to defects and performance issues.

Question 5: How does defect density affect gate fabrication design?

Defect density represents the number of defects per unit area on a semiconductor wafer. Minimizing defect density is critical for ensuring gate reliability and performance. High defect density can cause gate leakage, threshold voltage variation, and premature device failure.

Question 6: What is the purpose of simulation in gate fabrication design?

Simulation involves using computer models to predict gate performance before actual fabrication. It allows designers to identify and address potential issues early in the design process, optimize gate dimensions and materials, and ensure that the final product meets performance and reliability requirements.

Summary:Gate fabrication design plays a pivotal role in determining the performance, power consumption, and reliability of semiconductor chips. By carefully considering factors such as resolution, throughput, overlay accuracy, etch selectivity, defect density, and simulation, manufacturers can optimize gate designs to meet the demands of modern electronic devices.

Transition to the next article section:The following section will delve into advanced techniques and emerging trends in gate fabrication design, exploring innovative approaches to enhance chip performance and efficiency.

Gate Fabrication Design Tips

Optimizing gate fabrication design is crucial for enhancing the performance, power efficiency, and reliability of semiconductor chips. Here are several essential tips to guide your design process:

Tip 1: Prioritize Resolution and Overlay Accuracy

Higher resolution enables the creation of smaller gates, improving chip performance and reducing power consumption. Similarly, precise overlay accuracy ensures proper alignment of device layers, minimizing defects and enhancing reliability.

Tip 2: Optimize Etch Selectivity

Precisely controlling etch selectivity is essential for patterning gates, forming spacers, and creating contacts. Proper etch selectivity prevents damage to adjacent layers, reducing defects and ensuring device integrity.

Tip 3: Minimize Defect Density

Low defect density is crucial for gate reliability and performance. Employ high-quality materials, maintain a clean environment during fabrication, and implement stringent process control measures to minimize defects.

Tip 4: Consider Manufacturability

Designing gates with manufacturability in mind optimizes production efficiency and reduces costs. Choose materials and processes that are compatible with your fabrication capabilities, and consider the impact of design complexity on manufacturability.

Tip 5: Utilize Simulation Tools

Simulation allows you to predict gate performance before fabrication, enabling optimization of gate dimensions and materials. By identifying and resolving potential issues early, you can reduce design iterations and improve product yield.

Tip 6: Stay Updated with Advancements

Gate fabrication design is continuously evolving. Keep abreast of the latest techniques, such as extreme ultraviolet lithography and novel materials, to leverage advancements that enhance chip performance and efficiency.

Summary:By following these tips, you can optimize your gate fabrication design for improved device performance, reduced power consumption, and enhanced reliability. Remember to prioritize resolution, overlay accuracy, etch selectivity, defect density, manufacturability, and ongoing knowledge acquisition to stay at the forefront of gate fabrication design.

Transition to the article’s conclusion:These tips provide a solid foundation for gate fabrication design, empowering you to create high-quality semiconductor devices that meet the demands of modern electronics.

Conclusion

Gate fabrication design is a critical aspect of semiconductor manufacturing, underpinning the performance, power efficiency, and reliability of electronic devices. This article has extensively explored the key considerations and techniques involved in gate fabrication design, providing valuable insights for optimizing device performance.

By prioritizing factors such as resolution, overlay accuracy, etch selectivity, defect density, and manufacturability, designers can create gates that meet the stringent demands of modern electronics. Simulation tools further enhance design accuracy and efficiency, enabling the prediction and resolution of potential issues before fabrication. Staying abreast of advancements in gate fabrication design is also essential to leverage emerging techniques and materials that push the boundaries of chip performance.

As the electronics industry continues to advance rapidly, gate fabrication design will remain a cornerstone of innovation, enabling the development of smaller, faster, and more energy-efficient devices. By embracing the principles outlined in this article, designers can contribute to the creation ofsemiconductor technologies that drive technological progress and shape the future of electronics.